## LIN BOOTLOADER

#### 1. Relevant Devices

This application note applies to the following devices: C8051F50x, C8051F51x, C8051F54x, C8051F58x, and C8051F59x.

#### 2. Introduction

A bootloader enables field updates of application firmware. A Local Interconnect Network (LIN) bootloader enables firmware updates over the LIN bus. The LIN bootloader described in this application note is based on the Silicon Labs Modular Bootloader Framework. This framework is described in detail in the application note "AN533: Modular Bootloader Framework for Silicon Labs C8051Fxxx Microcontrollers", which can be downloaded from here: <a href="http://www.silabs.com/products/mcu/Pages/ApplicationNotes.aspx">http://www.silabs.com/products/mcu/Pages/ApplicationNotes.aspx</a>

The following components are part of the firmware update setup:

- Target Bootloader Firmware

- Master Programmer Firmware

- Active Data Source Software

- Application Firmware Image (Hex File)

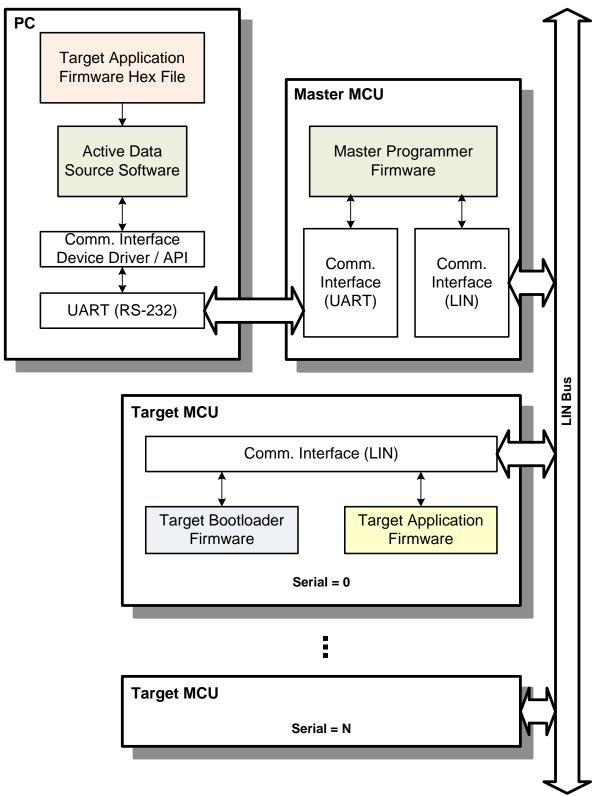

The firmware update setup is shown in Figure 1. Details about the steps involved in updating the firmware can be found in the Firmware Update Process Flow Diagram in application note AN533.

Figure 1. Firmware Update Setup

## 3. Target Bootloader Profile

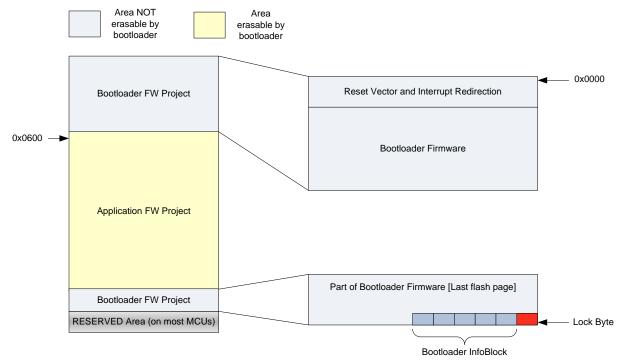

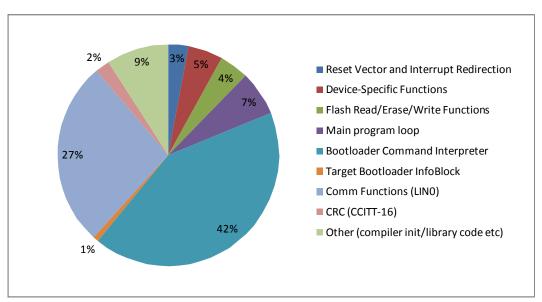

The LIN target bootloader firmware allows application firmware updates in the field over the LIN bus. The LIN bootloader code builds under the Keil toolchain with a total size of 1911 bytes. Because the bootloader and application have to be split on page boundaries, the bootloader takes up a total of 2 kB (= four flash pages) code space, with 512 bytes (= one flash page) of that total located on the last flash page, i.e., the one containing the lock byte. This means that the application firmware starts at address 0x0600 and ends one page short of the last flash page. Figure 2 shows the LIN bootloader memory map. Figure 3 shows the code space utilization of the bootloader grouped by functional blocks.

Figure 2. LIN Target Bootloader Memory Map

Figure 3. LIN Target Bootloader Code Space Utilization Profile

Rev. 0.1 3

## 3.1. Configurable Options

The target bootloader has the following parameters that can be configured. These parameters are located in two header files as grouped in Table 1 and Table 2.

Table 1. Fxxx\_Target\_Config.h

| Options                             |

|-------------------------------------|

| Any 8-bit value                     |

| 8-bit value: 0x82                   |

| Number of bytes per flash page: 512 |

| 8-bit value: 9                      |

| 24-bit value: 0x000600              |

| 24-bit value: 0x00FBFF              |

| Binary: 1                           |

| 8-bit value: 0x01                   |

| 8-bit value: 0x00                   |

|                                     |

#### Notes:

- 1. This can be used to identify a product line among many different products.

- 2. This denotes that the BL uses Silicon Labs-defined LIN bootloader protocol (see "Fxxx\_BL130\_LIN\_Interface.h").

- 3. Should be changed based on the MCU data sheet.

- **4.**  $2^n$  encoding:  $2^9 = 512$  bytes.

- 5. Starting address of App FW.

- 6. Ending address of App FW (includes App InfoBlock and Signature bytes).

- 7. 0 = Disabled; 1 = Enabled. When enabled, device serial number is matched for TGT\_ENTER\_BL\_MODE command.

- 8. Ensure a UNIQUE serial number for each device on the same LIN network.

4 Rev. 0.1

### Table 2. Fxxx\_TargetBL\_Config.h

| Parameter                                                      | Options                                              |

|----------------------------------------------------------------|------------------------------------------------------|

| CODE_BANKING                                                   | Binary: 0 <sup>1</sup>                               |

|                                                                | Binary: 1 <sup>2</sup>                               |

| BOOTLOADER_PIN_OVERRIDE <sup>3</sup>                           | Binary: 1                                            |

| TGT_BL_FW_INFOBLOCK_LENGTH <sup>4</sup>                        | 8-bit value: 16                                      |

| TGT_BL_FW_VERSION_LOW and TGT_BL_FW_VER-SION_HIGH <sup>5</sup> | 8-bit values: 0 and 1                                |

| TGT_BL_BUF_SIZE <sup>6</sup>                                   | Max number of bytes in bootloader receive buffer: 32 |

| TGT_BL_BUF_SIZE_CODE <sup>6</sup>                              | 8-bit value: 3                                       |

| TGT_CRC_TYPE <sup>7</sup>                                      | 8-bit value: 0x40                                    |

| TGT_BL_FW_INFOBLOCK_ADDR <sup>8</sup>                          | 24-bit value: 0x00FCFE                               |

#### Notes:

- 1. 0 = Disabled; 1 = Enabled. Disable for MCUs with flash memory 64 kB or less.

- 2. Enable for MCUs with flash memory greater than 64 kB.

- 3. 0 = Disabled; 1 = Enabled. When enabled, the bootloader will check a pin state on reset to see if it should stay in BL mode.

- 4. See Table 1 in AN533.

- 5. BL v1.0: Low = 0 and High = 1.

6. 2<sup>n</sup> encoding: 2<sup>3</sup> = 8 bytes.

- 7. This denotes that the BL uses the Silicon Labs-defined 16-bit CRC (CCITT-16) (see "Fxxx\_CRC064\_CCITT16.c").

- 8. Start address of BL InfoBlock so that it ends adjacent to the lock byte.

## 4. Target Application Profile

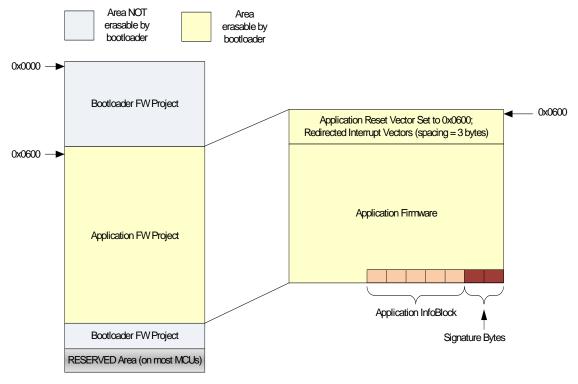

The target application firmware needs to fit within the allocated application area in flash memory. The application firmware memory map is shown in Figure 4.

Note: The application firmware starts at address 0x0600 in this example.

Figure 4. Target Application Memory Map

#### 4.1. Target Application Template

A target application template is included for easy integration with existing application code or to use as a starting point. This template includes the following files:

- Header Files

- Fxxx\_BL130\_LIN\_Interface.h

- Fxxx\_Target\_Config.h

- Fxxx\_Target\_Interface.h

- Fxxx\_TargetApp\_Config.h

- Source Files

6

- F50x\_TargetApp\_LIN0\_BLsupport.c

- F50x\_TargetApp\_Startup.A51

- Fxxx\_TargetApp\_InfoBlock.c

A typical application would use all files in the template, but that does not mean all the files in the template are required. Files can be omitted or used as a reference to create code that is more suitable to the application.

Rev. 0.1

#### 4.2. Configurable Options

The application firmware should always keep its version number updated in the Application InfoBlock whenever a new version is built so that the application hex file includes this information. The active data source software can interpret this information from the hex, while the master programmer can retrieve this data using the TGT Get Info command.

Table 3. Fxxx TargetApp Config.h

| Parameter                                                        | Options               |

|------------------------------------------------------------------|-----------------------|

| TGT_APP_FW_VERSION_LOW and TGT_APP_FW_VER-SION_HIGH <sup>1</sup> | 8-bit values: 0 and 1 |

| TGT_APP_FW_INFOBLOCK_LENGTH <sup>2</sup>                         | 8-bit value: 9        |

| Notes:                                                           |                       |

- **1.** App v1.0: Low = 0 and High = 1.

- 2. See Table 5 in AN533.

#### 4.3. Making an Application Bootloader Aware

A series of simple steps can be used to make an existing application firmware project "bootloader aware", i.e., allow it to co-exist with the bootloader. These steps are described in detail in AN533. The following is a summary of the changes needed when using the Keil toolchain for the 'F50x MCU family:

- 1. Add "F50x TargetApp Startup.A51" to application firmware project and build list; this changes the reset vector from 0x0000 to 0x0600.

- 2. Add these options to the compiler command line of the project: INTVECTOR(0x600) INTERVAL(3).

- 3. Add these options to the linker command line of the project: CODE(0x600-0xF9FD, ?CO?FXXX\_TARGETAPP\_INFOBLOCK(0xF9F4)).

- 4. Add 'Fxxx TargetApp InfoBlock.c' to the application project and build list.

- 5. [OPTIONAL] Add "F50x TargetApp LIN0 BLsupport.c" to the application project and build list, then insert calls in the application to call the functions in that source file to recognize the TGT Enter BL Mode command and take appropriate action.

- 6. Check hardware design to allow the use of a GPIO pin as a fail-safe trigger to enter bootload mode. In the LIN bootloader example, port pin P1.4 is used for this purpose. To disable or change this, see "Fxxx\_TargetBL\_Config.h" and "F50x\_TargetBL\_DevSpecific.c" in the Target Bootloader firmware project. If this is disabled, then the application has to provide some other way of entering bootload mode.

#### 4.4. Target Application Examples

Two versions of an application firmware example ("F50x\_LIN0\_Slave\_Blinky") are included with the source code. These examples show the application firmware settings needed to co-exist with the bootloader and also demonstrate firmware updates by showing slightly different functionality between the two versions (v1 and v1.1). See AN533 for the firmware update steps.

Rev. 0.1 7

# 5. Master Programmer and Data Source Examples

A master programmer example that runs on the C8051F500 MCU is included with the LIN bootloader source code. This master programmer example can update the firmware on any Silicon Labs MCU with a LIN interface that implements the LIN protocol as detailed in the above sections and per the specifications in Section 5. This example code can be used as-is, or can be used as a reference to implement this functionality on another MCU. The master programmer includes code to communicate with the active data source PC software via the UART. Code banking support is included, so the master programmer can work with targets that have more than 64 kB of flash memory. The Silicon Labs MCU Serial Bootloader Data Source software included with the modular bootloader framework is an example of an active data source software. This is described in application note "AN533: Modular Bootloader Framework for Silicon Labs C8051Fxxx Microcontrollers". The software installer and source code are included in the file "AN533SW.zip", which is available for download from: http://www.silabs.com/products/mcu/Pages/ApplicationNotes.aspx

## 6. LIN Protocol Details

Master Receive Message ID (Target to

Master)

The LIN protocol details used by the LIN bootloader are shown in Table 4. Any changes to these details would have to be duplicated in all three projects (Master Programmer, Target Bootloader, and Target Application). If changes are made to any of the protocol details, the "TGT\_BL\_TYPE" value in "Fxxx\_Target\_Config.h" should also be changed from the Silicon Labs standard value of 0x82 (decimal 130) to a value within the user-defined range of 0x01 through 0x7F, and the "130" in the file name "Fxxx\_BL130\_LIN\_Interface.h" should be changed appropriately as well.

**Parameter** Value **Parameter Definition and File Name** LIN Baud Rate 19200 Comm\_Init() function in F50x\_Comm\_LIN0.c Auto Baud Disabled Comm Init() function in F50x Comm LIN0.c LIN Message Size 8 bytes LIN MESSAGE SIZE in Fxxx\_BL130\_LIN\_Interface.h ID MASTER TO SLAVE BL CMD in Master Transmit Message ID (Master to 0x04 Target) Fxxx BL130 LIN Interface.h ID MASTER TO SLAVE WR CMD in Master Transmit Message ID (Master to 0x05

0x06

Fxxx\_BL130\_LIN\_Interface.h

Fxxx\_BL130\_LIN\_Interface.h

ID SLAVE TO MASTER BL RSP in

**Table 4. LIN Protocol Details**

www.silabs.com/loT

community.silabs.com

Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadio®, EZRadio®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701